- 您现在的位置:买卖IC网 > Sheet目录3890 > PIC16C717T-E/SS (Microchip Technology)IC MCU OTP 2KX14 A/D PWM 20SSOP

2002 Microchip Technology Inc.

DS41120B-page 125

PIC16C717/770/771

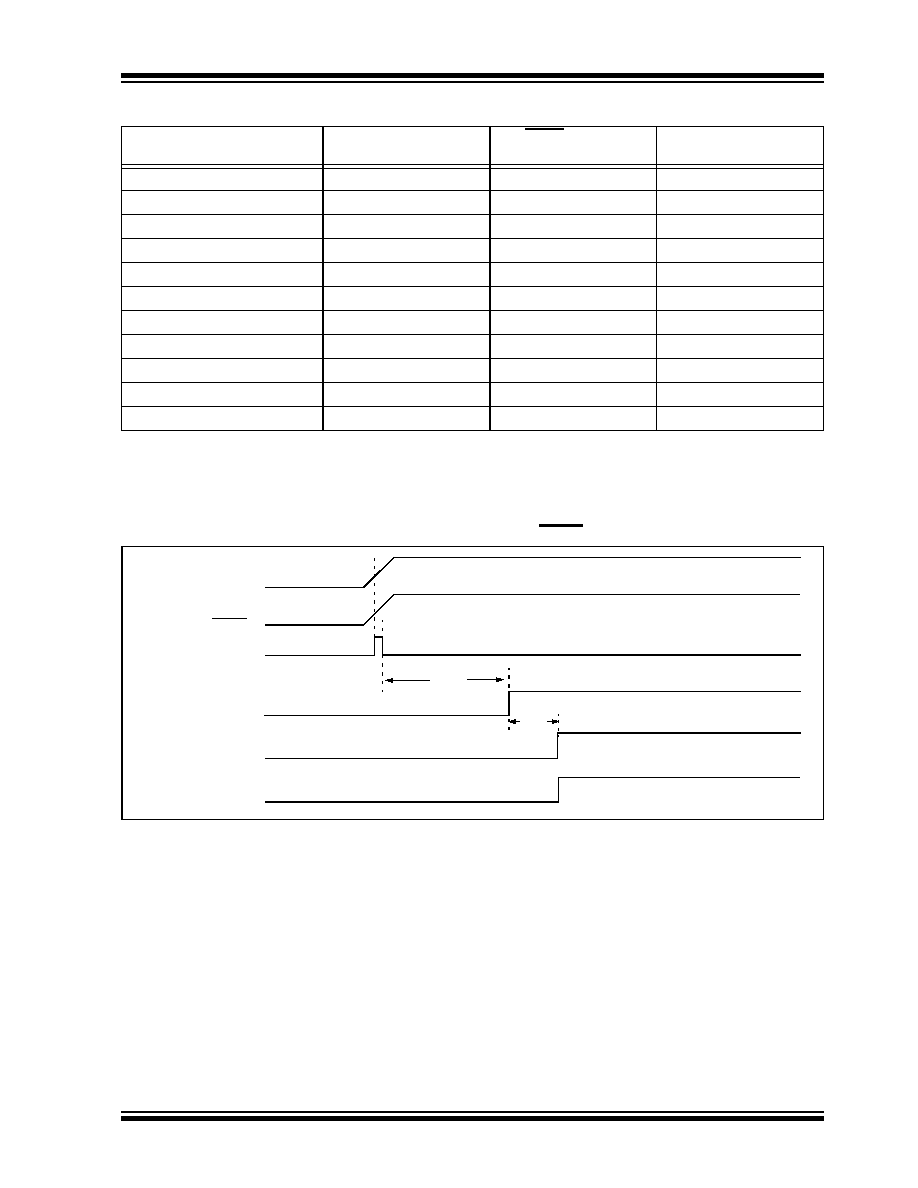

FIGURE 12-6:

TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

P1DEL

0000 0000

uuuu uuuu

REFCON

0000 ----

uuuu ----

LVDCON

--00 0101

--uu uuuu

ANSEL

--11 1111

--uu uuuu

ADRESL

xxxx xxxx

uuuu uuuu

ADCON1

0000 0000

uuuu uuuu

PMDATL

xxxx xxxx

uuuu uuuu

PMADRL

xxxx xxxx

uuuu uuuu

PMDATH

--xx xxxx

--uu uuuu

PMADRH

---- xxxx

---- uuuu

PMCON1

1--- ---0

TABLE 12-6:

INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

Register

Power-on Reset or

Brown-out Reset

MCLR Reset or

WDT Reset

Wake-up via WDT or

Interrupt

Legend: u = unchanged,

x

= unknown,

-

= unimplemented bit, read as ’0’, q = value depends on condition

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector

(0004h).

2: See Table 12-5 for RESET value for specific condition.

TPWRT

TOST

VDD

MCLR

INTERNAL POR

PWRT TIME-OUT

OST TIME-OUT

INTERNAL RESET

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LC770T-E/SO

IC MCU OTP 2KX14 A/D PWM 20SOIC

PIC16C771T/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

PIC16LC717T-I/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16C717T/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

PIC16LC770T-I/SO

IC MCU OTP 2KX14 A/D PWM 20SOIC

PIC16LC771T-E/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

PIC16C771T-E/SS

IC MCU OTP 4KX14 A/D PWM 20SSOP

PIC16LC771T-I/SO

IC MCU OTP 4KX14 A/D PWM 20SOIC

相关代理商/技术参数

PIC16C717T-I/SO

功能描述:8位微控制器 -MCU 3.5KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C717T-I/SS

功能描述:8位微控制器 -MCU 3.5KB 256 RAM 16 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O 4MHz SOIC18 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O 4MHz Ind Temp SOIC18 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-20/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C71T-20I/SO

功能描述:8位微控制器 -MCU 1.75KB 36 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C72/JW

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16C72-04/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT